## **BASYS3 board tutorial**

## (Decoder design using Vivado 2015.1)

Note: you will need the Xilinx Vivado Webpack version installed on your computer (or you can use the department systems).

This tutorial shows how to create a simple combinational design (a 3 to 8 decoder using the slider switches and leds) that can be implemented on the Basys3 board.

Start Vivado Design Suite:

Select Create New Project.

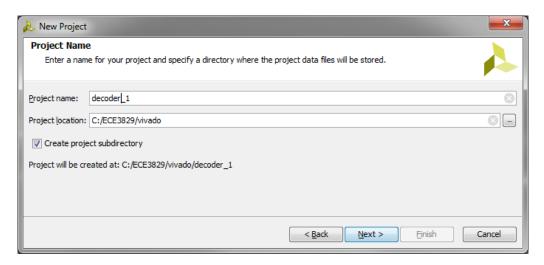

Click Next and then enter a Project name and location for your project:

1

Click Next and select the RTL project type:

| 🚴 New Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Project Type<br>Specify the type of project to create.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • |

| <ul> <li><u>RTL Project</u><br/>You will be able to add sources, create block designs in IP Integrator, generate IP, run RTL analysis, synthesis, implementation, design planning and analysis.</li> <li><u>Do not specify sources at this time</u></li> <li><u>Post-synthesis Project:</u> You will be able to add sources, view device resources, run design analysis, planning and implementation.</li> <li><u>Do not specify sources at this time</u></li> <li><u>I/O Planning Project</u></li> </ul> |   |

| < <u>Back</u> <u>Next</u> <u>Finish</u> Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ] |

Check the "Do not specify courses at this time" box and click Next:

Select the corect Xilinx FPGA that is on the Basys3 board (XC7A35T-1CPG236C)

| 🚴 New Project                                         |                          |                   |                  |                      |                | 1000             |                    | x       |

|-------------------------------------------------------|--------------------------|-------------------|------------------|----------------------|----------------|------------------|--------------------|---------|

| Default Part<br>Choose a default Xil<br>Select: Parts | inx part or bo<br>Boards | ard for your proj | ject. This can b | e changed later.     |                |                  |                    |         |

| Product category:                                     | All                      |                   | -                | Package:             | cpg236         |                  | •                  |         |

| Eamily:                                               | Artix-7                  |                   | Ŧ                | Spee <u>d</u> grade: | -1             |                  | •                  |         |

| Sub-Family:                                           | Artix-7                  |                   | *                | Temp grade:          | С              | c 🗸              |                    |         |

|                                                       |                          |                   |                  | Si Revision:         | All Remain     | ning             | •                  |         |

| Search: Q-                                            |                          |                   | Reset            | All Filters          |                | - ber            |                    |         |

| Part                                                  | I/O Pin<br>Count         | Available<br>IOBs | LUT<br>Elements  | FlipFlops            | Block<br>RAMs  | DSPs             | Gb<br>Transceivers | G<br>TI |

| 🔷 xc7a15tcpg236-1                                     | 236                      | 106               | 10400            | 20800                | 25             | 45               | 2                  | 2       |

| xc7a35tcpg236-1<br>xc7a50tcpg236-1                    | 236<br>236               | 106<br>106        | 20800<br>32600   | 41600<br>65200       | 50<br>75       | 90<br>120        | 2<br>2             | 2       |

| •                                                     | III                      |                   |                  |                      |                |                  |                    |         |

|                                                       |                          |                   |                  | < <u>B</u> ack       | <u>N</u> ext > | > <u>F</u> inish | Cance              |         |

Click Next, and then Finish:

| 🚴 New Project                       |                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | New Project Summary                                                                                                                                                                             |

| VIVADO.                             | <ol> <li>A new RTL project named 'decoder_1' will be created.</li> </ol>                                                                                                                        |

|                                     | <ol> <li>The default part and product family for the new project:<br/>Default Part: xc7a35tcpg236-1<br/>Product: Artix-7<br/>Family: Artix-7<br/>Package: cpg236<br/>Speed Grade: -1</li> </ol> |

| <b>EXILINX</b><br>ALL PROGRAMMABLE- | To create the project, dick Finish                                                                                                                                                              |

|                                     | < Back Next > Einish Cancel                                                                                                                                                                     |

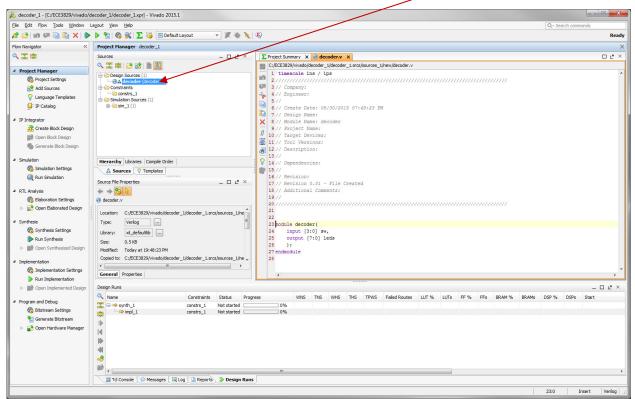

The Project window opens:

| 🚴 decoder_1 - [C:/ECE3829/vivado/d                                | decoder_1/decoder_1_xpr] - Vivado 2015.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | x   |  |  |  |  |  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| Ele Edit Flow Tools Window Lagout Yew Help                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| 達 🔄 📾 🦇 🏬 📉 🔸 🔈 👌 🌀 🛞 🔽 🌀 🗄 Default.tayott 🔷 🎉 🛞 😵 😵 😵 Ready      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| Flow Navigator V Project Hanager-decode_1 X                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| 오 🖫 🖨                                                             | Sources _ L L X D Project Summary X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |  |  |  |  |  |

| Project Manager                                                   | x = i and i                                       | *   |  |  |  |  |  |

| St Add Sources<br>V Language Templates                            | Constant Criterian Cr |     |  |  |  |  |  |

| IP Integrator                                                     | Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | *   |  |  |  |  |  |

| Create Block Design                                               | Status: Not started Status: Not started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |  |  |  |  |  |

| Generate Blick Design                                             | Messages: No errors or warnings Messages: No errors or warnings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

|                                                                   | Hierarchy         Librais         Comple Order         Part:         xc7a35tpg236-1           Part:         xc7a35tpg236-1         Part:         xc7a35tpg236-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| <ul> <li>Simulation</li> </ul>                                    | A Sources Templates Strategy: Windo Synthesis Defaults Incrementation Defaults Incrementation Defaults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |  |  |  |  |  |

| 🔞 Simulation Settings                                             | Properties _ L 2 ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |  |  |  |  |

| ( Run Simulation                                                  | ← + 10 k<br>DRC Volations & Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | *   |  |  |  |  |  |

| # RTI Analysis                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ^   |  |  |  |  |  |

| C Elaboration Settings                                            | Run Implementation to see DRC results Run Implementation to see timing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |  |  |  |  |  |

| Open Elaborated Design                                            | 2 Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | *   |  |  |  |  |  |

| 4 Synthesis                                                       | Select an object to see properties Utilization X Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *   |  |  |  |  |  |

| 🔞 Synthesis Settings                                              | Run Synthesis to see utilization results Run Implementation to see power results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |  |  |  |

| 🗞 Run Synthesis                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| Open Synthesized Design                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| 4 Implementation                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| (5) Implementation Settings                                       | Design Runs L 2<br>Q Name Constraints Status Progress WNS THS WHS THS TPWS Failed Routes LUT % LUTs FF % FFs BRAM % BRAMs DSP % DSPs Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _   |  |  |  |  |  |

| Run Implementation                                                | Name     Constraints Status Progress     WINS THS WINS THS THYS Failed Routes LUT% LUT% FP % FPs BRAM % BRAM % BSP % DSP % DSP % Start     Start     Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 1 |  |  |  |  |  |

| Open Implemented Design                                           | we mpi 1 constrs 1 Not started 0%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |  |  |  |  |

| 4 December and Datum                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |  |  |  |  |

| <ul> <li>Program and Debug</li> <li>Bitstream Settings</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| Cenerate Bitstream                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| Open Hardware Manager                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 1 |  |  |  |  |  |

|                                                                   | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 1 |  |  |  |  |  |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •   |  |  |  |  |  |

|                                                                   | Td Console 🗋 Messages 🔄 Log 🗋 Reports 🔪 🗩 Design Runs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _   |  |  |  |  |  |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

| l                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |  |

We now need to add a Verilog design source to describe our decoder operation.

Click on Add Sources in the left Project Manager window (or select the menu item File => Add Sources:

| Add Sources |                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------|

| VIVADO.     | Add Sources This guides you through the process of adding and creating sources for your project |

|             | <ul> <li>Add or greate constraints</li> <li>Add or create design sources</li> </ul>             |

|             | <ul> <li>Add or create simulation sources</li> <li>Add or create DSP sources</li> </ul>         |

|             | <ul> <li>Add existing block design sources</li> <li>Add existing IP</li> </ul>                  |

| XILINX      | To continue, click Next                                                                         |

|             | < Back Next > Einish Cancel                                                                     |

Select Next,

And then select Create File (click on the + symbol) and enter decoder for the file name: