### **Instructions:**

- 1. This Quiz is closed book and closed notes.

- 2. You may have pens, pencils, erasers, a calculator, and a water bottle/drink.

- 3. Electronic devices are **NOT ALLOWED** during this Quiz, with the exception of a calculator. **You shall NOT share a calculator with others during the Quiz.**

- 4. Place your student ID card on your desk for us to review.

- 5. When you are finished, remain in your seat and raise your hand and we will come and collect your **Quiz**. You must not talk to anyone in the room until your Quiz has been collected, and you have left the room.

- 6. Any form of cheating/academic integrity violation, including (but not limited to) violation of the rules above will result in an automatic 0 for the Quiz.

### Please fill your name in the blank and sign the statement below:

I,\_\_\_\_\_

have read, and acknowledge that I will adhere to the instructions above and if not followed, I will accept the penalty given by the instructor.

Signature: \_\_\_\_\_

# STOP!! PLEASE DO NOT START THE QUIZ

Q2: \_\_\_\_\_6 points

# UNTIL YOU ARE TOLD TO DO SO

# FOR GRADERS ONLY:

- Q1: \_\_\_\_\_6 points Q4: \_\_\_\_\_10 points

- Q5: \_\_\_\_\_10 points

- Q3: \_\_\_\_\_6 points Q6: \_\_\_\_\_12 points

Total: \_\_\_\_\_50 points

#### [Question 1] (6 Points)

Consider the following list of instructions. Assume that the initial values for \$s1, \$s2 and \$s3 are all 10:

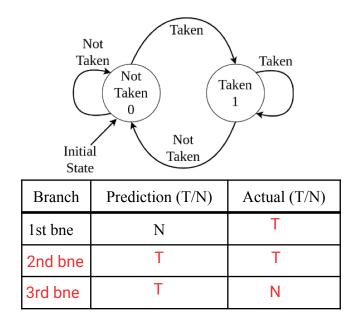

|       | bne \$s3, \$s1, loop | s1 !=s3               | s1 !=s3           | s1 ==s3           |

|-------|----------------------|-----------------------|-------------------|-------------------|

|       | addi \$s3, \$s3, -3  |                       | s3 = 5 - 3 = 2    | s3 = 4 - 3 = 1    |

|       | sub \$s3, \$s3, \$s2 | s3 = 10 - 3 = 7       | s3 = 4 - (-1) = 5 | s3 = 2 - (-2) = 4 |

|       | sub \$s2, \$s2, \$s1 | s2 = 10 - 7 = 3       | s2 = 3 - 4 = -1   | s2 = -1 - 1 = - 2 |

| loop: | addi \$s1, \$s1, -3  | s1 = 10 - 3 = 7       | s1 = 7 - 3 = 4    | s1 = 4 - 3 = 1    |

|       |                      | <u>1st Iteration:</u> | 2nd Iteration:    | 3rd Iteration:    |

Assume that we have a 1-bit branch predictor that stores the result of the last branch and makes the prediction based on the result. Show the results of all predictions throughout the execution. (Use T/N to represent Taken/Not Taken)

### [Question 2] (6 Points)

a. If a direct-mapped cache has a hit rate of 90%, a hit time of 2 ns, and a miss penalty of 100 ns, what is the AMAT (Average Memory Access Time)?

```

AMAT = Hit Time + Miss Rate × Miss Penalty

= 2 + (0.10 × 100)

= 2 + 10

= 12 ns

```

b. If an L2 cache is added with a hit time of 10 ns and a hit rate of 60%, what is the new AMAT? Miss penalty stays the same.

```

AMAT = L1 Hit Time + L1 Miss Rate × (L2 Hit Time + L2 Miss Rate × Miss Penalty)

= 2 + 0.1 × (10 + 0.4 × 100)

= 2 + 5

= 7 ns

```

c. If replacing the L1 cache with a 2-way set associative increases the hit rate to 95%, but increases the hit time to 3 ns, what is the new AMAT? Miss penalty stays the same Assume (b) does not apply. (there is no L2 cache)

```

AMAT = Hit Time + Miss Rate × Miss Penalty

= 3 + (0.05 \times 100)

= 3 + 5

= 8 \text{ ns}

```

# [Question 3] (6 Points)

Write-through and write-back are approaches used when there is a cache hit.

Explain how write-through and write-back work. Highlight the pros and cons of each.

Write-back: Handles writes by updating only to the block in the cache. The modified cache block is written to main memory only when it is replaced.

Advantages:

(i) Low latency

(ii) High throughput for write-intensive applications

Disadvantages: There is a risk of losing data if the cache is overwritten without backing up in the lower memory. Since such overwrites cannot be done, writes either take 2 cycles or use a write buffer, meaning either increased latency or increased complexity/overhead.

Write-through: Handles writes by updating both the block in the cache and the block in main memory.

Advantages:

(i) Easier to implement

- (ii) Read misses never result in writes to the lower level

- (iii) Data coherency/consistency

Disadvantages: Higher latency from multiple writes to the lower-level memory.

### [Question 4] [10 Points]

Assuming 32-bit memory addresses, how many bits are associated with the tag, index, and offset of the following configurations for a byte-addressable direct mapped cache?

- a. 32 blocks, 8 bytes per block Offset Bits =  $\log_2(8) = 3$ Index Bits =  $\log_2(32) = 5$ Tag Bits = 32-3-5 = 24

- b. 16 blocks, 4 bytes per block Offset Bits =  $\log_2(4) = 2$ Index Bits =  $\log_2(16) = 4$ Tag Bits = 32-2-4 = 26

# [Question 5] (10 Points)

A processor with Instruction cache miss rate of 3% and Data cache miss rate of 5% and costs 10 cycles on a cache miss (miss penalty). 50% of the instructions to be executed are Load and Store instructions. The CPI with ideal cache (no misses) is 3.

```

a. Compute the actual CPI

Given:

Instruction-cache miss rate = 3%

Data-cache miss rate = 5%

Miss penalty = 10 cycles

Instruction-cache: Miss rate ×

Miss penalty = 0.03 × 10 = 0.3

Base CPI (with ideal cache performance) = 3

Load & stores are 50% of instructions Miss

cycles per instruction

Data-cache: 0.50 × 0.05 × 10 = 0.25

```

Actual CPI = 3 + 0.3 + 0.25 = 3.55

b. Consider the datapath was improved so that the CPI can be reduced from 3 to 2 (all the other specs remain the same). Compute the actual CPI and compare it with (a).

- For this part, we assume that the ideal CPI is reduced to 2 but the miss penalties remain the same.

- Effective CPI = 2 + 0.3 + 0.25 = 2.55

The improved datapath reduces the CPI from 3.55 to 2.55, significantly speeding up performance and enhancing processor efficiency compared to previous one.

# [Question 6] (12 Points)

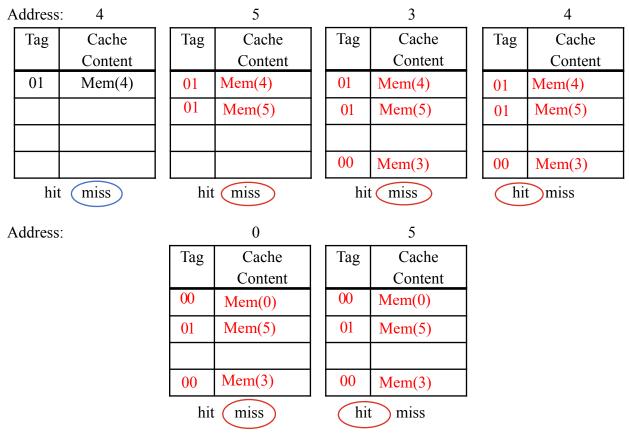

a) Consider a direct-mapped cache of size 4 Bytes. Each block in the cache can hold only 1 word (here 1 word = 1 Byte). Fill in the missing cache blocks at each step according to the address reference, and specify whether it is a hit or a miss. The first step has been done for you. Address references are (in order): 4, 5, 3, 4, 0, 5

b) Calculate the miss rate for the above (Part a.)

Miss rate = (Total misses)/(Total references)

```

= 4/6

```

= 0.67 or 67%