# CSE 486/586 Distributed Systems Cache Coherence

### Steve Ko

Computer Sciences and Engineering University at Buffalo

CSF 486/586

### **Storage to Memory**

- · We've looked at storage consistency.

- The same consistency models are equally applicable to memory.

- Think multiple threads accessing the same memory

- But a memory system can have another form of consistency mainly for managing caches. We'll look at this today.

- In a multi-core system, there are many caches, and they need to be synchronized.

SF 486/586

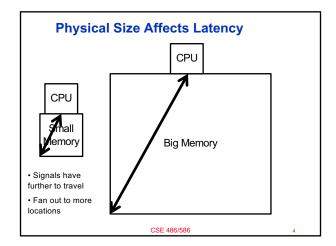

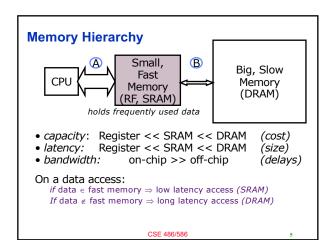

# Performance of high-speed computers is usually limited by memory bandwidth & latency • Latency (time for a single access) Memory access time >> Processor cycle time Problematic • Bandwidth (number of accesses per unit time)

Increase the bus size, etc.

Usually OK

### **Administrivia**

- · PA3 grading still going on

- This Friday, no recitation, undergrad office hours from 2 pm – 4 pm & general office hours from 4 pm – 5 pm

CSE 486/586

### **Cache Coherence**

- A cache coherence protocol ensures that all writes by one processor are eventually visible to other processors

- i.e., updates are not lost

- You can consider this a hardware-based update propagation mechanism for distributed caches.

- Hardware support is required such that

- only one processor at a time has write permission for a location

- no processor can load a stale copy of the location after a write

CSE 486/586

11

### **Cache Coherence**

- A memory system is coherent if:

- A read by a processor P to a location X that follows a write by P to X, with no writes of X by another processor occurring between the write and the read by P, always returns the value written by P.

- A read by a processor to location X that follows a

write by another processor to X returns the written

value if the read and write are sufficiently separated

in time and no other writes to X occur between the

two accesses.

- Writes to the same location are serialized; that is, two writes to the same location by any two processors are seen in the same order by all processors.

- (Coherence provides per-location sequential consistency).

CSE 486/586

C 2

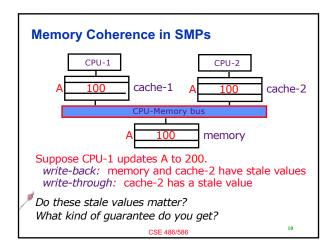

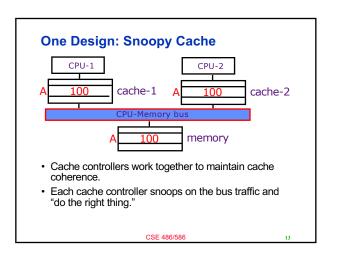

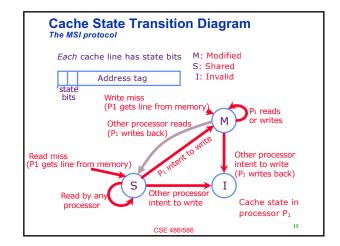

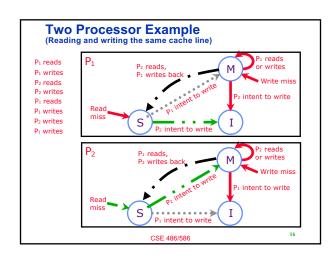

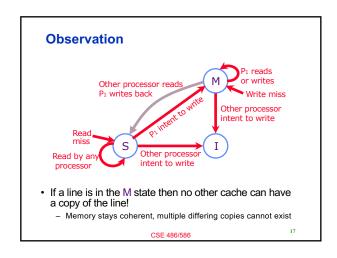

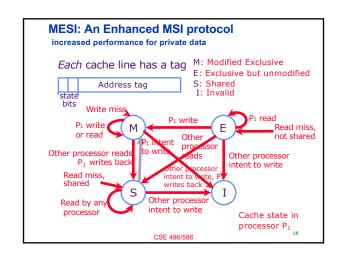

### **Snoopy Cache Coherence Protocol** • For a read operation, a cache line is shared across multiple caches. • For a write operation, a cache line is not shared. · Fach cache line has a state: - M (modified): the processor has written to it. - S (shared): other caches have a copy as well. - I (invalid): the data is no longer valid. · Writing to a cache line - If it's M, the cache controller does the write. If it is not M, it sends an invalidation request to other caches, switches the state to M, and does the write. - Other cache controllers switch the state to I. · Reading a memory address - If it's a hit, read it. - If it's not a hit, read it from memory, and other cache controllers switch the state to S.

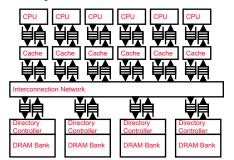

## **Scalable Approach: Directories**

- Every memory block has associated directory information

- keeps track of copies of cached blocks and their states

- on a miss, find directory entry, look it up, and communicate only with the nodes that have copies if necessary

- in scalable networks, communication with directory and copies is through network transactions

- · Many alternatives for organizing directory information

CSE 486/586

19

# **Basic Operation of Directory**

- k processors.

- With each cache-block in memory: k presence-bits, 1 dirty-bit

- With each cache-block in cache: 1 valid bit, and 1 dirty (owner) bit

- Read from main memory by processor i:

- If dirty-bit OFF then { read from main memory; turn p[i] ON; }

- if dirty-bit ON then { recall line from dirty proc (downgrade cache state to shared); update memory; turn dirty-bit OFF; turn p[i] ON; supply recalled data to i;}

- Write to main memory by processor i:

**Directory Cache Protocol**

Assumptions: Reliable network, FIFO message delivery between any given source-destination pair

CSE 486/586

### **Cache States**

For each cache line, there are 4 possible states:

- C-invalid (= Nothing): The accessed data is not resident in the cache.

- C-shared (= Sh): The accessed data is resident in the cache, and possibly also cached at other sites. The data in memory is valid.

- C-modified (= Ex): The accessed data is exclusively resident in this cache, and has been modified. Memory does not have the most up-to-date data.

- C-transient (= Pending): The accessed data is in a transient state (for example, the site has just issued a protocol request, but has not received the corresponding protocol reply).

CSE 486/586

22

### **Home directory states**

- For each memory block, there are 4 possible states:

- R(dir): The memory block is shared by the sites specified in dir (dir is a set of sites). The data in memory is valid in this state. If dir is empty (i.e., dir =  $\epsilon$ ), the memory block is not cached by any site.

- W(id): The memory block is exclusively cached at site id, and has been modified at that site. Memory does not have the most up-to-date data.

- TR(dir): The memory block is in a transient state waiting for the acknowledgements to the invalidation requests that the home site has issued.

- TW(id): The memory block is in a transient state waiting for a block exclusively cached at site id (i.e., in C-modified state) to make the memory block at the home site up-todate.

CSE 486/586

23

### Summary

- · Cache coherence

- Making sure that caches do not contain stale copies.

- · Snoopy cache coherence

- MSI

- MESI

- · Directory-based

- Uses a directory per memory bank

CSE 486/586

/586

C

# Acknowledgements

- These slides heavily contain material developed and copyright by

Krste Asanovic (MIT/UCB)

- David Patterson (UCB)

- And also by:

- Arvind (MIT)

- Joel Emer (Intel/MIT)

- James Hoe (CMU)

- John Kubiatowicz (UCB)

- MIT material derived from course 6.823

- UCB material derived from course CS252

С 5