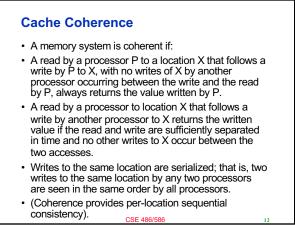

## **Cache Coherence**

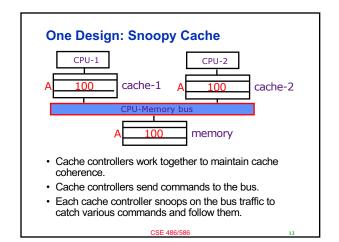

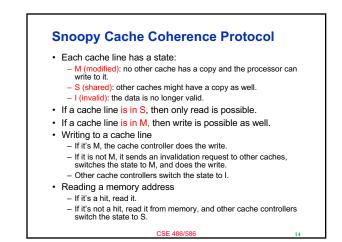

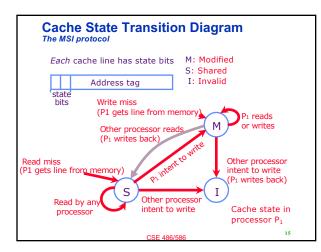

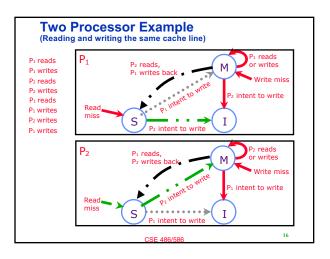

- A cache coherence protocol ensures that all writes by one processor are eventually visible to other processors

- i.e., updates are not lost

- You can consider this a hardware-based update propagation mechanism for distributed caches.

- Hardware support is required such that

only one processor at a time has write permission

- for a location

- no processor can load a stale copy of the location after a write

CSE 486/586

п

## **Acknowledgements**

- These slides heavily contain material developed and copyright by

- Krste Asanovic (MIT/UCB)

- David Patterson (UCB)

- And also by:

- Arvind (MIT)

- Joel Emer (Intel/MIT)

- James Hoe (CMU)

- John Kubiatowicz (UCB)

- MIT material derived from course 6.823

- UCB material derived from course CS252

CSE 486/586