#### Write-Back Cache Accesses

- · Write-back cache

- Writes only go to cache (make *dirty* lines)

Upon evict, update memory

- 0 mem access

- Write hit

- 1 mem access

- Read miss on a clean line

- 2 mem accesses

- Read miss on a dirty line

- Variable cycles per read/write, might complicate the pipeline control

CSE 490/590, Spring 2011

CSE 490/590, Spring 2011

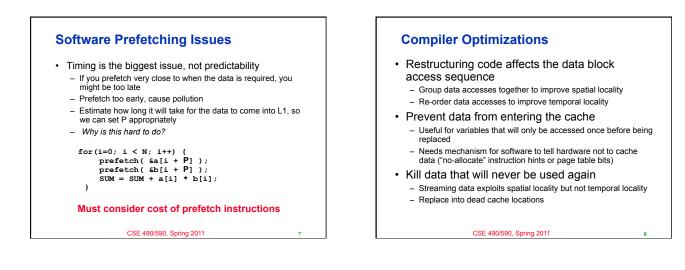

## Software Prefetching

```

for(i=0; i < N; i++) {

prefetch( &a[i + 1] );

prefetch( &b[i + 1] );

SUM = SUM + a[i] * b[i];

}</pre>

```

What property do we require of the cache for prefetching to work ?

CSE 490/590, Spring 2011

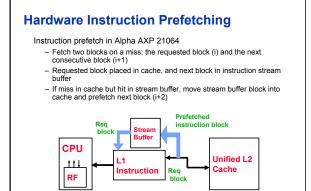

# One Block Lookahead (OBL) scheme Initiate prefetch for block b + 1 when block b is accessed Why is this different from doubling block size? Can extend to N-block lookahead Strided prefetch If observe sequence of accesses to block b, b+N, b+2N, then prefetch b+3N etc. Example: IBM Power 5 [2003] supports eight independent streams of strided prefetch per processor, prefetching 12 lines ahead of current access

Hardware Data Prefetching

-Prefetch b + 1 upon miss on b

· Prefetch-on-miss:

CSE 490/590, Spring 2011

### CSE 490/590 Administrivia

- Midterm on Friday, 3/4

- Project 1 deadline: Friday, 3/11

- Guest lectures possibly this month

- Course early-evaluation today

CSE 490/590, Spring 2011

13

### Acknowledgements

- These slides heavily contain material developed and copyright by Krste Asanovic (MIT/UCB)

David Patterson (UCB)

- And also by:

- Arvind (MIT)

- Joel Emer (Intel/MIT)

James Hoe (CMU)

- John Kubiatowicz (UCB)

- MIT material derived from course 6.823

- UCB material derived from course CS252

CSE 490/590, Spring 2011

14