# Week 5

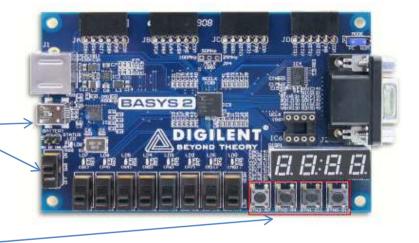

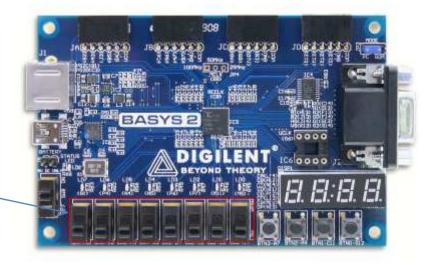

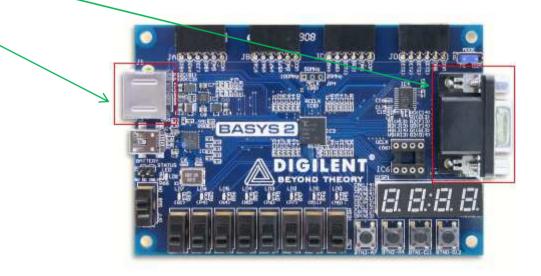

# I/O on the BASYS 2 Board

- Power Supply

- Switch Selectable (SW8)

- Options

- USB

- External (3.5VDC 5.5VDC Power Supply)

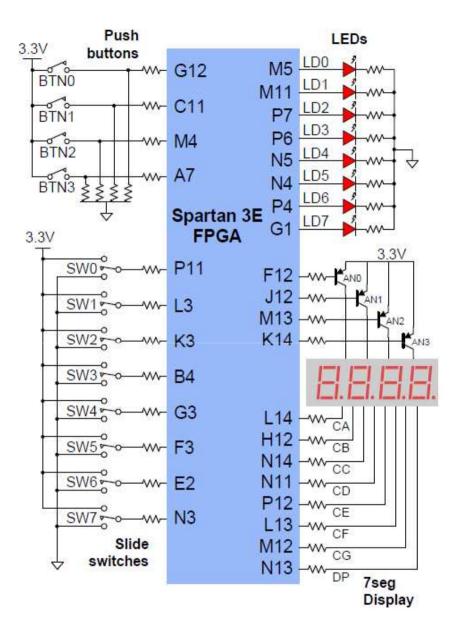

### • Pushbuttons

- Four Pushbuttons

- Normally low

- Driven high when button is pressed

- Short Circuit Protection Provided

- Connecting FPGA pin as output could result in short circuit

- Remedied with resistor

- Refer to page 4 of BASYS 2 Reference Manual

- Slider Switches

- Eight Slider Switches

- Constant high or low signal

- Short Circuit Protection Provided

- Connecting FPGA pin as output could result in short circuit

- Remedied with resistor

- Refer to page 4 of BASYS 2 Reference Manual

- LEDs

- Eight LEDs –

- Anodes driven from FPGA

- Logic 1 illuminates LED

- Cathodes connected to ground via resistor

- Refer to page 4 of BASYS 2 Reference Manual

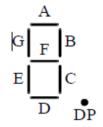

### • Seven-Segment Displays

- Four Seven-Segment Displays

- Common Anode

- Enabling Digits

- AN0...AN3

- Active Low

- When enabled, cathodes (CA, CB, ..., CF, CG, DP) can be driven

- Low signal illuminates segment

- Illuminating multiple digits with different values

- All digits can APPEAR continuously illuminated if driven once every 1 to 16 ms (1 KHz to 60 Hz)

- Refer to pages 4-5 of BASYS 2 Reference Manual

## • Oscillators

- Primary Oscillator

- User selectable (soldering required)

- 25, 50, or 100 MHz

- Refer to page 3 of BASYS Reference Manual

- CLK1

- Pin B8 of FPGA

- Secondary Oscillator

- Socket provided

- CLK2

## • PS/2 &VGA Port

– PS/2 & VGA Ports Available

To display Number "1" on First Segment , then we need to have: - AN1 to be activated which means "0" (active low) - CB, CC are activated which means "0" and every other pins to be inactivated which means "1"

### Basys2 I/O circuits

# Managing a Large Project

#### • Managing a Large Project

- Tasks

- Functions

- Modules

- Tasks

- Can enable other tasks & functions

- May execute in non-zero simulation time

- May contain delay, event, or timing control statements

- May have zero or more arguments

- Туре

- Input

- Output

- Inout

- Can pass values, but do NOT return a value

- Syntax

- Definition

- task Task\_Name; input, Output, & Local Variable List begin body end endtask

- Call

Task\_Name(Argument\_List);

### • Functions

- Can enable another function

- Not a task

- Execute in zero simulation time

- Can NOT contain

- A delay event

- Timing control statements

- Must have at least one input argument

- Always return a single value

- Output & InOut arguments NOT allowed

- Syntax

- Definition

function Function\_Name; // Note name may represent a vector Input & Local Variable List

begin

Body - Note the output must be assigned a value end

endfunction

• Call

Function\_Name(Argument\_List);

# **Tasks & Functions**

- Local to the module

- They can contain

- Local variables

- Registers

- Time Variables

- Integers

- Reals

- Events

- Cannot contain

- Wires

- Always Blocks

- Initial Blocks

- Behavioral only!

# Modules

• Instantiating modules can help make code easier to write, modify, read, and debug

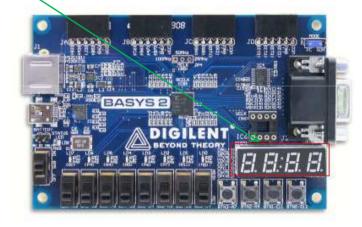

# **Strobe Example**

- Description

- The number '12' is displayed on the middle two digits of the 7segment display

- LED blinks at the frequency used to strobe the 7-segment display

- Reset

- Switch 0

- When low, the 7-segment display is disabled

- When high, '12' is displayed on the 7-segment display

- Pin Assignments

- Reset (P11)

- Clock (B8)

- LD0 (M5)

- Anodes 1...4 (F12, J12, M13, K14)

- Seg A...G (L14, H12, N14, N11, P12, L13, M12)

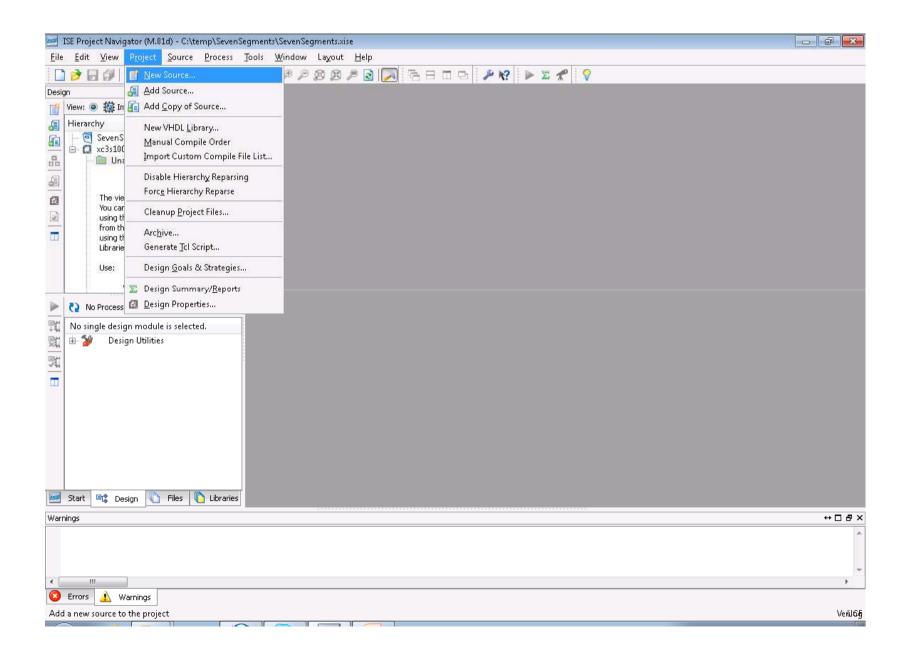

- In this example we are going to download Nonvolatile Designs to the FPGA PROM on the BASYS 2 Board

- If you are going to Print your design on PROM you **don't** need to change the clock to JTAG

### - Open the ISE project Navigator

-

| 🗺 ISE Project Navigator (M.81d)                                                                                                         | - 6 💌 |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew P <u>r</u> oject <u>S</u> ource <u>P</u> rocess <u>T</u> ools <u>W</u> indow Layout <u>H</u> elp |       |

|                                                                                                                                         |       |

| Start ↔ □ ♂ ×                                                                                                                           |       |

| Welcome to the ISE® Design Suite                                                                                                        |       |

| Project commands                                                                                                                        |       |

| Open Project Project Browser                                                                                                            |       |

|                                                                                                                                         |       |

| New Project Open Example                                                                                                                |       |

| Recent projects                                                                                                                         |       |

| Double click on a project in the list below to open                                                                                     |       |

| safiwan777                                                                                                                              |       |

| Safiwan123                                                                                                                              |       |

| MainProject1 project4                                                                                                                   |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

| Additional resources                                                                                                                    |       |

| ISE Design Suite InfoCenter                                                                                                             |       |

| Key New Features in Project Navigator<br>Tutorials on the Web                                                                           |       |

| Design Resources                                                                                                                        |       |

| Application Notes                                                                                                                       |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

| Warnings                                                                                                                                | ⇔⊡₽×  |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

|                                                                                                                                         |       |

| ✓ III                                                                                                                                   |       |

| 😢 Errors 🔬 Warnings                                                                                                                     |       |

### - Type the project name

|   |                              | ×                                |  |

|---|------------------------------|----------------------------------|--|

|   | 🚾 New Project Wi             | zard                             |  |

| C | Create New Pro               | ject                             |  |

| s | pecify project location      | n and type.                      |  |

|   | -Enter a name, locati        | ons, and comment for the project |  |

|   | N <u>a</u> me:               | SevenSegments                    |  |

|   | Location:                    | C:\temp\SevenSegments            |  |

|   | Working Directory:           | C:\temp\SevenSegments            |  |

|   | Description:                 |                                  |  |

|   |                              |                                  |  |

|   |                              |                                  |  |

|   |                              |                                  |  |

|   |                              |                                  |  |

|   |                              |                                  |  |

|   | Select the tupe of to        | p-level source for the project   |  |

|   | <u>T</u> op-level source typ |                                  |  |

|   | Schematic                    |                                  |  |

|   | L                            |                                  |  |

| M | ore Info                     | <u>N</u> ext Cancel              |  |

### - Select these options then click next

| Project Settings                                                                       |                     |

|----------------------------------------------------------------------------------------|---------------------|

| Specify device and project properties.<br>Select the device and design flow for the pr | roject              |

| Property Name                                                                          | Value               |

| Product Category                                                                       | All                 |

| Family                                                                                 | Spartan 3E          |

| Device                                                                                 | XC3S100E            |

| Package                                                                                | CP132 .             |

| Speed                                                                                  | -5                  |

| Top-Level Source Type                                                                  | Schematic           |

| Synthesis Tool                                                                         | XST (VHDL/Verilog)  |

| Simulator                                                                              | ISim (VHDL/Verilog) |

| Preferred Language                                                                     | Verilog             |

| Property Specification in Project File                                                 | Store all values    |

| Manual Compile Order                                                                   |                     |

| VHDL Source Analysis Standard                                                          | VHDL-93             |

| Enable Message Filtering                                                               |                     |

|                                                                                        |                     |

|                                                                                        |                     |

#### - click finish

| 🚱 🔤 New Project Wizard                                                         |

|--------------------------------------------------------------------------------|

| Project Summary                                                                |

| Project Summary                                                                |

| Project Navigator will create a new project with the following specifications. |

| Project:                                                                       |

| Project Name: SevenSegments                                                    |

| Project Path: C:\temp\SevenSegments                                            |

| Working Directory: C:\temp\SevenSegments                                       |

| Description:                                                                   |

| Top Level Source Type: Schematic                                               |

| Device:                                                                        |

| Device Family: Spartan3E                                                       |

| Device: xc3s100e                                                               |

| Package: cp132                                                                 |

| Speed: -5                                                                      |

| Synthesis Tool: XST (VHDL/Verilog)                                             |

| Simulator: Modelsim-PE Mixed                                                   |

| Preferred Language: Verilog                                                    |

| Property Specification in Project File: Store all values                       |

| Manual Compile Order: false                                                    |

| VHDL Source Analysis Standard: VHDL-93                                         |

| Message Filtering: disabled                                                    |

|                                                                                |

|                                                                                |

|                                                                                |

| More Info                                                                      |

#### - Select Project $\rightarrow$ new source

- Select Verilog module and write the file name, then click next

| 🚾 New Source Wizard                                                                                                                                                                                                                                                                                     |                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Select Source Type, file name and its location.  Select source type, file name and its location.  Select Source type, file name and its location.  Schematic User Document User Document Verilog Module Verilog Test Fixture VHDL Module VHDL Library VHDL Package VHDL Test Bench  Sembedded Processor | File name:<br>SevenSegModule<br>Location:<br>C:\temp\SevenSegments |

| More Info                                                                                                                                                                                                                                                                                               | Next Cancel                                                        |

#### - click next

| Define Module              |          |   |     |     |     |

|----------------------------|----------|---|-----|-----|-----|

| Specify ports for module.  |          |   |     |     |     |

| Module name SevenSegModule |          |   |     |     |     |

| Port Name                  | Directio | n | Bus | MSB | LSB |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

|                            | input    | - |     |     |     |

#### - Click Finish

|                                                                                                                                | ×   |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 🚱 🔤 New Source Wizard                                                                                                          |     |

| Summary                                                                                                                        |     |

| _ Project Navigator will create a new skeleton source with the following specifications.                                       |     |

| Add to Project: Yes<br>Source Directory: C:\temp\SevenSegments<br>Source Type: Verilog Module<br>Source Name: SevenSegModule.v |     |

| Module name: SevenSegModule<br>Port Definitions:                                                                               |     |

|                                                                                                                                |     |

|                                                                                                                                |     |

|                                                                                                                                |     |

|                                                                                                                                |     |

| More Info                                                                                                                      | :el |

#### - The file will be created and it will look like as below

| ISE      | ISE Project Navigator (M.81d) - C:\temp\SevenS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ments\SevenSegments.                                                                                                                                                                    | xise - [SevenSegModule.v]                                                                                                                                                             |                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|          | Eile <u>E</u> dit <u>V</u> iew P <u>r</u> oject <u>S</u> ource <u>P</u> roces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>T</u> ools <u>W</u> indow Lay                                                                                                                                                        | iout <u>H</u> elp                                                                                                                                                                     | - 8 ×                 |

|          | o al 🗶 🗇 🖧 👹 🖓 📢 📢 📢                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | » 🏓 🏓 👧 🙉                                                                                                                                                                               | 🏓 🗟 🔀 🖻 🗗 🖻 🥬 🛠? 🕨 🗶 🗶 💡                                                                                                                                                              |                       |

|          | yn ↔ □ ♂ ×<br>View:<br>Wiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yiew:<br>Yi | 2 /////<br>3 // Com<br>4 // Eng<br>5 //<br>6 // Cre<br>7 // Des<br>8 // Mod<br>9 // Pro<br>10 // Tar<br>11 // Too<br>12 // Des<br>13 //<br>14 // Dep<br>15 //<br>16 // Rev<br>17 // Rev | ate Date: 19:10:47 02/13/2011<br>ign Name:<br>ule Name: SevenSegModule<br>ject Name:<br>get Devices:<br>l versions:<br>cription:<br>endencies:<br>ision:<br>ision 0.01 - File Created |                       |

| ►<br>III | No Processes Running Processes: SevenSegModule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19 //<br>20 //////                                                                                                                                                                      | itional Comments:<br>////////////////////////////////////                                                                                                                             |                       |

|          | Processes: Seversegwindule<br>Design Summary/Reports<br>Design Utilities<br>User Constraints<br>Synthesize - XST<br>Implement Design<br>Generate Programming File<br>Configure Target Device<br>Analyze Design Using ChipScope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22 );<br>23<br>24<br>25 endmod<br>26                                                                                                                                                    |                                                                                                                                                                                       |                       |

| 150      | Start 💷 Design 🐚 Files 🐚 Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SevenS                                                                                                                                                                                  | egModule.v 🔀 🔀 Design Summary 🔀                                                                                                                                                       | •                     |

|          | nings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                         | ognodaorr 🖬 🔤 borgin banning y                                                                                                                                                        | ↔□ਰ×                  |

| ••••     | III (JS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                         |                                                                                                                                                                                       |                       |

| 1        | Errors 🔔 Warnings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                         |                                                                                                                                                                                       | n 21 Col 23 Verkil66j |

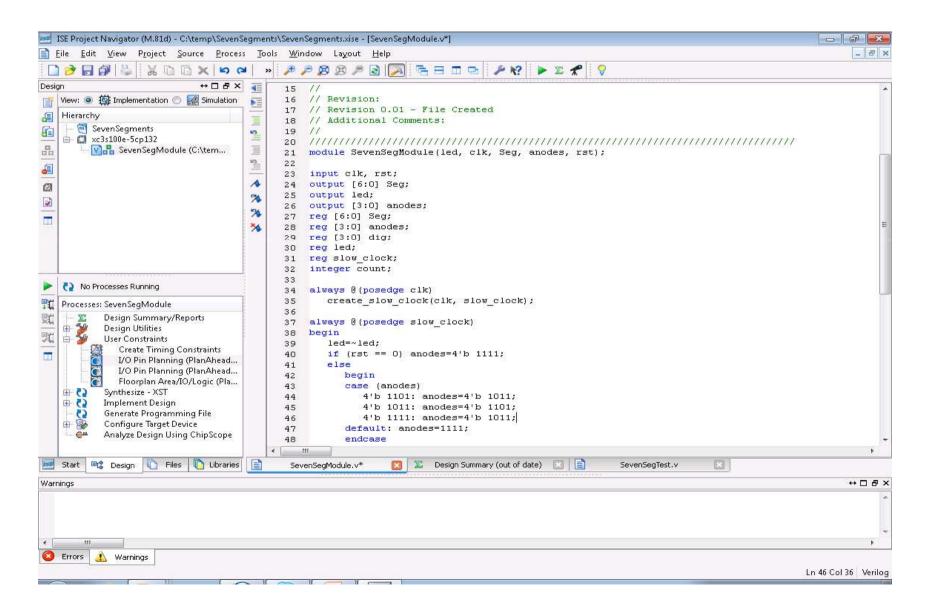

#### - Add your code

$\sim$

| ISE        | ISE Project Navigator (M.81d) - C:\temp\SevenS                                                                                                                                                                                                                 | Segments\SevenSegments.xise - [SevenSegModule.v]                                                                                                                                                                                                                                                                                                                                        | - 6 .             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <b>B</b> . | ile <u>E</u> dit <u>V</u> iew P <u>r</u> oject <u>S</u> ource <u>P</u> roces                                                                                                                                                                                   | ss <u>T</u> ools <u>W</u> indow Layout <u>H</u> elp                                                                                                                                                                                                                                                                                                                                     | - 8 ×             |

|            | o 🕶 🗶 🚺 🖓 😓 🕷 🖬 🍯                                                                                                                                                                                                                                              | 🛤 » 🏓 🔊 🕼 🏓 💽 🦰 🗄 🗖 🖙 🥬 🛠? 🕨 🕱 🛠 💡                                                                                                                                                                                                                                                                                                                                                      |                   |

|            | yn ↔ □ ₽ ×<br>View:                                                                                                                                                                                                                                            | <pre>3 // Company:<br/>4 // Engineer:<br/>5 //<br/>6 // Create Date: 15:44:31 02/13/2011<br/>7 // Design Name:<br/>8 // Module Name: sfaaa<br/>9 // Project Name:<br/>10 // Target Devices:<br/>11 // Tool versions:<br/>12 // Description:<br/>13 //<br/>14 // Dependencies:<br/>15 //<br/>16 // Revision:<br/>17 // Revision 0.01 - File Created<br/>18 // Additional Comments:</pre> | E                 |

|            | No Processes Running                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| - PC       | Processes: SevenSegModule                                                                                                                                                                                                                                      | 21 22                                                                                                                                                                                                                                                                                                                                                                                   |                   |

|            | <ul> <li>Design Summary/Reports</li> <li>Design Utilities</li> <li>User Constraints</li> <li>Synthesize - XST</li> <li>Implement Design</li> <li>Generate Programming File</li> <li>Configure Target Device</li> <li>Analyze Design Using ChipScope</li> </ul> | <pre>23 24 module SevenSegModule(led, clk, Seg, anodes, rst); 25 26 input clk, rst; 27 output [6:0] Seg; 28 output led; 29 output [3:0] anodes; 30 reg [6:0] Seg; 31 reg [3:0] anodes; 32 reg [3:0] dig; 33 reg led; 34 reg slow_clock; 35 integer count; 4</pre>                                                                                                                       | •                 |

| ISE        | Start 🔍 Design 🚺 Files 陷 Libraries                                                                                                                                                                                                                             | SevenSegModule.v 🙁 Design Summary                                                                                                                                                                                                                                                                                                                                                       |                   |

| Erro       | s                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                         | ⇔⊡∄×              |

|            |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                         | *                 |

| •          | III                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                         | ¥.                |

| 8          | Errors 🔬 Warnings                                                                                                                                                                                                                                              | Ln                                                                                                                                                                                                                                                                                                                                                                                      | 80 Col 10 Verilog |

module SevenSegModule(led, clk, Seg, anodes, rst);

```

input clk, rst;

output [6:0] Seg;

output led;

output [3:0] anodes;

reg [6:0] Seg;

reg [3:0] anodes;

reg [3:0] dig;

reg led;

reg slow_clock;

integer count;

always @(posedge clk)

create slow clock(clk, slow clock);

always @(posedge slow clock)

begin

led=~led;

if (rst == 0) anodes=4'b 1111;

else

begin

case (anodes)

4'b 1101: anodes=4'b 1011;

4'b 1011: anodes=4'b 1101;

```

```

4'b 1111: anodes=4'b 1011;

default: anodes=1111;

endcase

case (anodes)

4'b 1011: dig=1;

4'b 1101: dig=2;

endcase

case (dig)

1: Seg = 7'b 1111001;

2: Seg = 7'b 0100100;

endcase

end

end

task create_slow_clock;

input clock;

inout slow_clock;

integer count;

begin

if (count > 250000)

begin

count=0;

slow_clock = ~slow_clock;

end

count = count+1;

end

endtask

endmodule

```

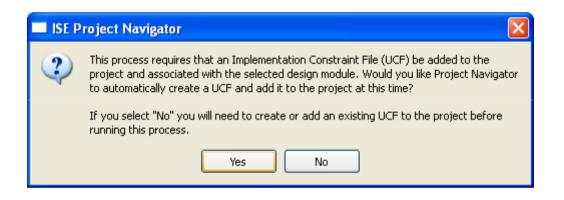

-To implement the code on the fpga board go to implementation mode -- Select circuit.v file and select I/O planning (Planhead-Presynthesis ) to open Planahead application to assign the fpga I/O ports to the code I/O

- Click yes to create UCF file and open Planahead application

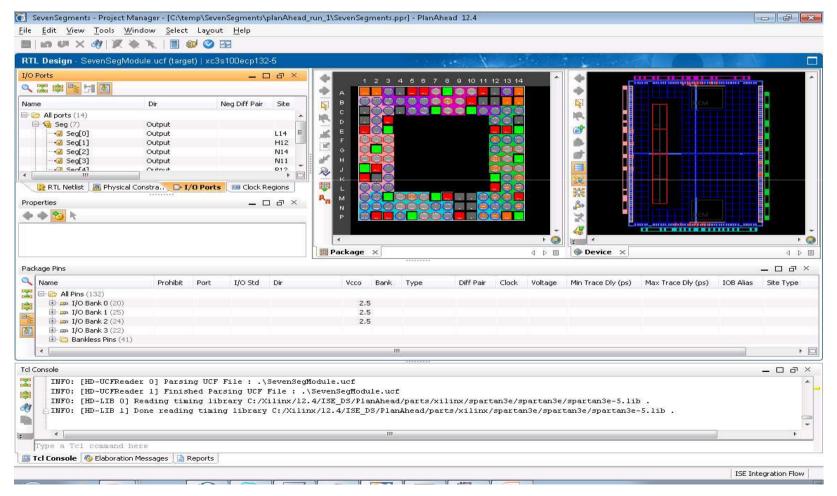

-Planahead Application after its opened

-Select I/O ports, drag and drop each of them to Pin in the Package figure, refer to <u>http://www.digilentinc.com/Data/Products/BASYS2/Basys2 rm.pdf</u> to find the pin definition

-- Click save design and exit

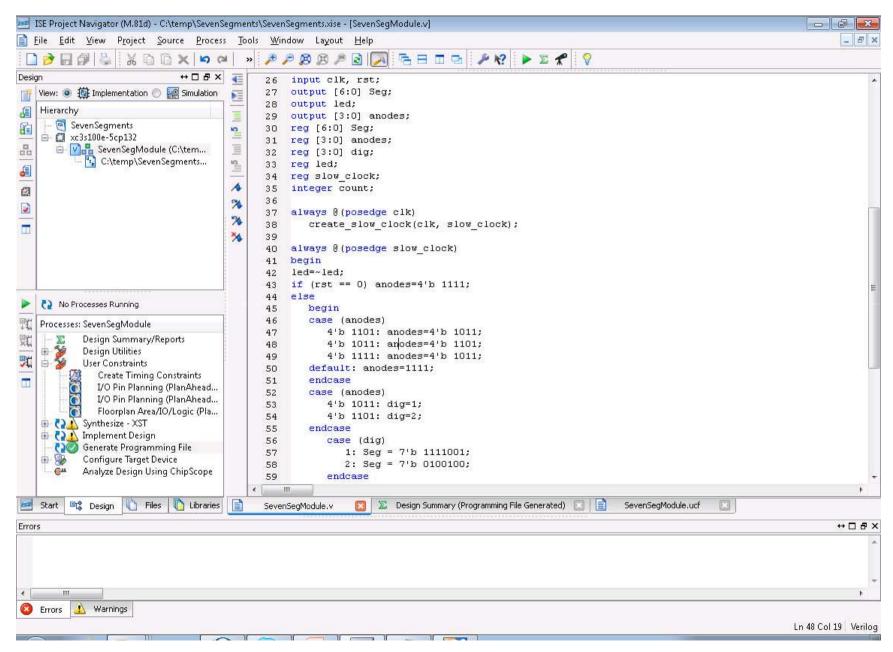

## Create the *.bit file,* Double click on *Generate Programming File in the Processes* Window

| 🐖 ISE Project Navigator (M.81d) - C:\temp\SevenS                                                                                                                                                                                                                                                                                                                                                                                                    | gments\SevenSegments.xise - [SevenSegModule.v]                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 📄 <u>F</u> ile <u>E</u> dit <u>V</u> iew P <u>r</u> oject <u>S</u> ource <u>P</u> rocess                                                                                                                                                                                                                                                                                                                                                            | <u>T</u> ools <u>W</u> indow Layout <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                           | _ 8 ×                |

| ○ ○ ○ ○ × ○ ○ × ○ ○                                                                                                                                                                                                                                                                                                                                                                                                                                 | » 🔑 🔑 🛞 🔎 🗟 🏹 🖙 🗄 🗉 🕞 🤌 🛠? 🕨 🗵 🛠 💡                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| Design       ↔ □ ♂ ×         View: ● ☆ Implementation ●  Simulation         Hierarchy         □ ☆ xc3s100e-5cp132         ● ☆ xc3s100e-5cp132         ● ☆ SevenSegModule (C:\tem         ○ ☆ C:\temp\SevenSegments                                                                                                                                                                                                                                  | <pre>24 module SevenSegModule(led, clk, Seg, anodes, rst);<br/>25<br/>26 input clk, rst;<br/>27 output [6:0] Seg;<br/>28 output led;<br/>29 output [3:0] anodes;<br/>30 reg [6:0] Seg;<br/>31 reg [3:0] anodes;<br/>32 reg [3:0] dig;<br/>33 reg led;<br/>34 reg slow_clock;<br/>35 integer count;<br/>36<br/>37 always @(posedge clk)<br/>38 create_slow_clock);<br/>39<br/>40 always @(posedge slow_clock)</pre>                                         |                      |

| <ul> <li>Running: Generate Bitstream</li> <li>Processes: SevenSegModule</li> <li>Design Summary/Reports<br/>Design Utilities</li> <li>User Constraints<br/>U/O Pin Planning (PlanAhead<br/>I/O Pin Planning (PlanAhead<br/>I/O Pin Planning (PlanAhead<br/>Floorplan Area/IO/Logic (Pla<br/>Synthesize - XST</li> <li>Synthesize - XST</li> <li>Generate Programming File<br/>Configure Target Device<br/>Analyze Design Using ChipScope</li> </ul> | <pre>41 begin<br/>42 led=~led;<br/>43 if (rst == 0) anodes=4'b 1111;<br/>44 else<br/>45 begin<br/>46 case (anodes)<br/>47 4'b 1101: anodes=4'b 1011;<br/>48 4'b 1011: anodes=4'b 1101;<br/>49 4'b 1111: anodes=4'b 1011;<br/>50 default: anodes=1111;<br/>51 endcase<br/>52 case (anodes)<br/>53 4'b 1011: dig=1;<br/>54 4'b 1101: dig=2;<br/>55 endcase<br/>56 case (dig)<br/>57 1: Seg = 7'b 1111001;<br/>4 10 11 10 11 11 11 11 11 11 11 11 11 11</pre> |                      |

| Start 🕫 Design 🚺 Files 🚺 Libraries                                                                                                                                                                                                                                                                                                                                                                                                                  | SevenSegModule.v 🛛 🖾 Design Summary (Implemented) 🛛 📄 SevenSegModule.ucf 🔍                                                                                                                                                                                                                                                                                                                                                                                 |                      |

| Errors                                                                                                                                                                                                                                                                                                                                                                                                                                              | and a second and a second a se                                                                                                                                                                                                                                                                                                                                            | ↔□₽×                 |

| < III                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| 🙆 Errors 🔔 Warnings                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ln 42 Col 10 Veriloo |

#### Make sure that every thing is compiling and building

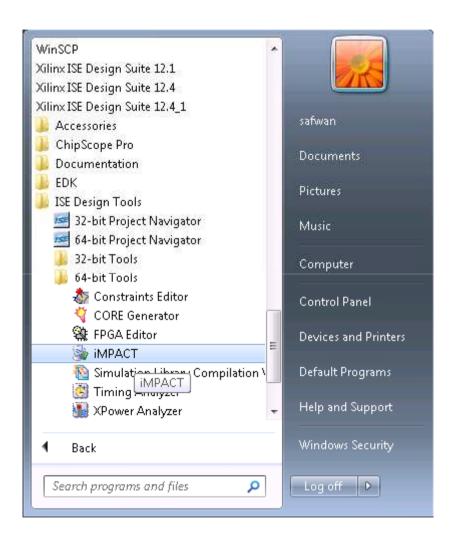

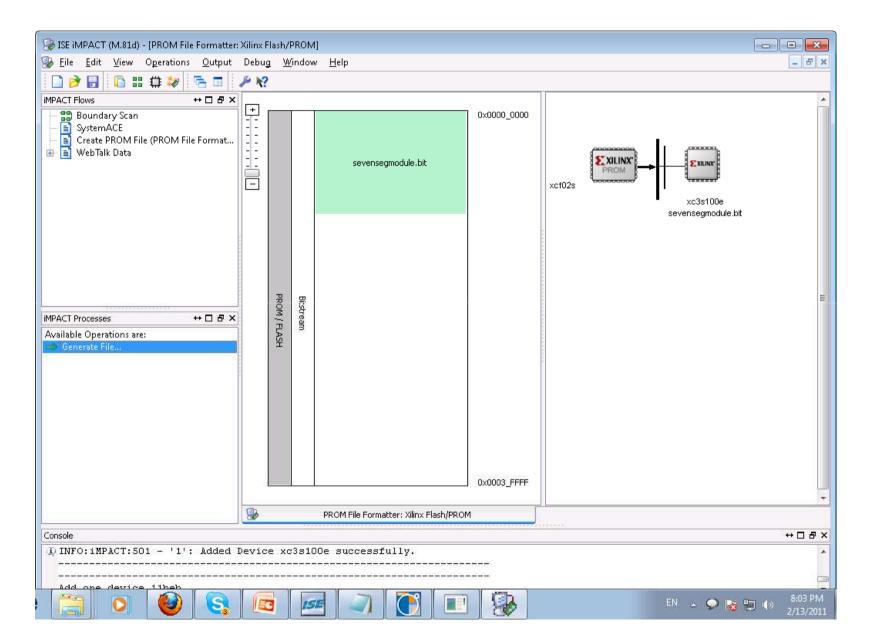

#### Open iMPACT application from Xillinx ISE Deisgn Suite 12.4 tools

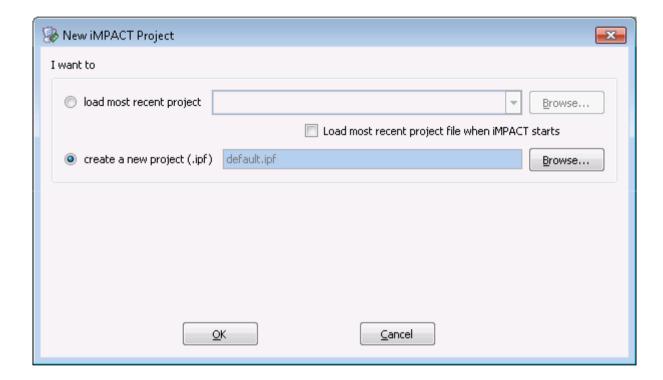

#### **Create New Project**

In the Welcome to iMPACT popup window, select Prepare a PROM File and click on OK

| 🛞 Welcome to iMPACT                                                 | × |  |  |  |  |

|---------------------------------------------------------------------|---|--|--|--|--|

| Please select an action from the list below                         |   |  |  |  |  |

| Configure devices using Boundary-Scan (JTAG)                        |   |  |  |  |  |

| Automatically connect to a cable and identify Boundary-Scan chain 📼 |   |  |  |  |  |

| Prepare a PROM File                                                 |   |  |  |  |  |

| Prepare a System ACE File                                           |   |  |  |  |  |

| Prepare a Boundary-Scan File                                        |   |  |  |  |  |

| SVF 👻                                                               |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

| OK                                                                  |   |  |  |  |  |

|                                                                     |   |  |  |  |  |

### - Select Xilinx Flash/PROM

- Click on the green arrow

| 🛞 PROM File Formatter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ×                        |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Step 1. Select Storage Target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Step 2, Add Storage Device(s)                                                                                                | Step 3,                                                                                                                                                                                                                                                                                                                                                                                                                                         | Enter Data               |  |  |

| Storage Device Type :<br>Xlinx Flash/PROM<br>Spartan3AN<br>Spartan3AN<br>Configure Single FPGA<br>Configure MultiBoot FPGA<br>Configure Single FPGA<br>Configure MultiBoot FPGA<br>Configure MultiBoot FPGA<br>Configure from Paralleled PROMs<br>Generic Parallel PROM                                                                                                                                                                                                                                             | Target FPGA       Spartan3E         Storage Device (bits):       512K         Add Storage Device       Remove Storage Device | General File Detail         Checksum Fill       FF         Output File Name       Untitled         Output File Name       C:\Xilinx\12.4         Output File Format       C:\Xilinx\12.4         Flash/PROM File Property       File Format         Use Power-of-2 for Start Addr       Number of Bitstream         Bitstream 0 Start Address       Bitstream 1 Start Address         Add Non-Configuration Data File       Number of Data File | Value  BIN No 2 0 675840 |  |  |

| Description:         The PROM File Formatter will guide you through the steps to format bitstream BIT files into a PROM file that is compatible with Xilinx® and third-party PROM programmers. The programmed PROM device can then be used to configure the target FPGA.         Additional capabilities of the PROM File Formatter include:         • Generating PROM files containing specific EPG0 configuration instructions required to support daisy-chained EPG0 bitstream BIT files         OK       Cancel |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |  |  |

#### -Select *Platform Flash under PROM Family* -Select *xcf02s under Device* -Click on *Add Storage Device* -Click on the green arrow

| 😵 PROM File Formatter        |                                                                                                                  |                                                                                                                                  | ×                                  |

|------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Step 1. Select Storage Targe | t Step 2. Add Storage Device(s)                                                                                  | Step 3,                                                                                                                          | Enter Data                         |

| Storage Device Type :<br>    | PROM Family     Platform Flash       Device (bits)     xcf02s       Add Storage Device     Remove Storage Device | General File Detail<br>Checksum Fill<br>Value<br>Output File Name<br>Output File                                                 | Value<br>d<br>Ix\12.4\<br>P<br>BIN |

|                              | Auto Select PROM                                                                                                 | Number of Bitstream<br>Bitstream 0 Start Address<br>Bitstream 1 Start Address<br>Add Non-Configuration Da<br>Number of Data File | 2<br>0<br>675840<br>ta Files Yes   |