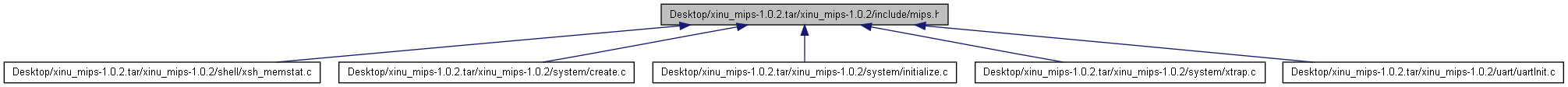

Desktop/xinu_mips-1.0.2.tar/xinu_mips-1.0.2/include/mips.h File Reference

Go to the source code of this file.

Detailed Description

Define human readable registers, coprocessor 0 registers, cause and status register masks, memory segment addresses, context record offsets, and cache functions and register offsets.

- Id

- mips.h 235 2007-07-12 22:52:09Z agember

Definition in file mips.h.

Define Documentation

argument 0 to 3

Definition at line 23 of file mips.h.

asm temp - uppercase because of ".set at"

Definition at line 20 of file mips.h.

| #define CAUSE_EXC 0x0000007C |

Cause register interrupt masks Exception Code

Definition at line 96 of file mips.h.

| #define CAUSE_HW0 0x00000400 |

Hardware interrupt

Definition at line 99 of file mips.h.

| #define CAUSE_HW1 0x00000800 |

UART interrupt

Definition at line 100 of file mips.h.

| #define CAUSE_HW2 0x00001000 |

| #define CAUSE_HW3 0x00002000 |

| #define CAUSE_HW4 0x00004000 |

| #define CAUSE_HW5 0x00008000 |

Timer interrupt

Definition at line 104 of file mips.h.

| #define CAUSE_SW0 0x00000100 |

Software interrupt

Definition at line 97 of file mips.h.

| #define CAUSE_SW1 0x00000200 |

data cache

Definition at line 158 of file mips.h.

Cache register locations within the Config1 register instruction cache

Definition at line 155 of file mips.h.

value mask

Definition at line 161 of file mips.h.

Context record offsets context record size in bytes context record size in words

Definition at line 136 of file mips.h.

| #define CONTEXT_WORDS (CONTEXT / sizeof(long)) |

Bad address generated by TLB exceptions

Definition at line 64 of file mips.h.

Identifies cause of interrupt/exception

Definition at line 69 of file mips.h.

interrupt when CP0_COUNT == CP0_COMPARE

Definition at line 67 of file mips.h.

configuration register (select 0, 1)

Definition at line 72 of file mips.h.

Hold PTE base and VPN on TLB exception

Definition at line 61 of file mips.h.

Timer counter

Definition at line 65 of file mips.h.

implementation dependent (diagnostic?)

Definition at line 73 of file mips.h.

Hi half of TLB (VPN+ASID)

Definition at line 66 of file mips.h.

Even page TLB entry

Definition at line 59 of file mips.h.

Odd page TLB entry

Definition at line 60 of file mips.h.

Return address after exception handling

Definition at line 70 of file mips.h.

Coprocessor 0 registers Index pointer into TLB

Definition at line 57 of file mips.h.

Mask for virtual address on TLB matching

Definition at line 62 of file mips.h.

processor identification

Definition at line 71 of file mips.h.

Random pointer into TLB

Definition at line 58 of file mips.h.

Various run time processor information

Definition at line 68 of file mips.h.

Boundary between random and wired entries

Definition at line 63 of file mips.h.

| #define FILL_I_CACHE 0x14 |

fill instruction cache

Definition at line 167 of file mips.h.

frame pointer

Definition at line 50 of file mips.h.

frame pointer

Definition at line 150 of file mips.h.

global pointer

Definition at line 48 of file mips.h.

global pointer

Definition at line 149 of file mips.h.

| #define INDEX_STORE_TAG_D 0x9 |

invalidate data cache tag

Definition at line 168 of file mips.h.

| #define INDEX_STORE_TAG_I 0x8 |

Cache functions invalidate instruction cache tag

Definition at line 166 of file mips.h.

PIC jump register

Definition at line 45 of file mips.h.

kernel scratch

Definition at line 46 of file mips.h.

| #define KSEG0_BASE 0x80000000 |

| #define KSEG0_SIZE 0x20000000 |

kernel unmapped, cahced (512 MB)

Definition at line 127 of file mips.h.

| #define KSEG1_BASE 0xA0000000 |

kernel unmapped, uncached base

Definition at line 128 of file mips.h.

| #define KSEG1_SIZE 0x20000000 |

kernel unmapped, uncached (512 MB)

Definition at line 129 of file mips.h.

| #define KSEG2_BASE 0xC0000000 |

kernel mapped base

Definition at line 130 of file mips.h.

| #define KSEG2_SIZE 0x40000000 |

kernel mapped (1 GB)

Definition at line 131 of file mips.h.

| #define KUSEG_BASE 0x00000000 |

Define kernel memory segments for MIPS32 processors userspace mapped base

Definition at line 124 of file mips.h.

| #define KUSEG_SIZE 0x80000000 |

userspace mapped (2 GB)

Definition at line 125 of file mips.h.

| #define PRID_CPUID 0x0000FF00 |

CPU ID

Definition at line 82 of file mips.h.

| #define PRID_REV 0x000000FF |

| #define PRID_REV_WRT350N 0x1A |

| #define PRID_REV_WRT54G 0x29 |

| #define PRID_REV_WRT54GL 0x08 |

return address

Definition at line 52 of file mips.h.

| #define RA_CON (CONTEXT - 8) |

return address

Definition at line 140 of file mips.h.

callee saved 0 to 7

Definition at line 35 of file mips.h.

callee saved registers

Definition at line 141 of file mips.h.

same like fp!

Definition at line 51 of file mips.h.

stack pointer

Definition at line 49 of file mips.h.

| #define STATUS_ERL 0x00000004 |

Error Level

Definition at line 111 of file mips.h.

| #define STATUS_EXL 0x00000002 |

Exception Level

Definition at line 110 of file mips.h.

| #define STATUS_HW0 CAUSE_HW0 |

Hardware interrupt enable

Definition at line 114 of file mips.h.

| #define STATUS_HW1 CAUSE_HW1 |

UART interrupt enable

Definition at line 115 of file mips.h.

| #define STATUS_HW2 CAUSE_HW2 |

| #define STATUS_HW3 CAUSE_HW3 |

| #define STATUS_HW4 CAUSE_HW4 |

| #define STATUS_HW5 CAUSE_HW5 |

Timer interrupt enable

Definition at line 119 of file mips.h.

| #define STATUS_IE 0x00000001 |

Status register masks Global interrupt enable

Definition at line 109 of file mips.h.

| #define STATUS_SW0 CAUSE_SW0 |

Software interrupt enable

Definition at line 112 of file mips.h.

| #define STATUS_SW1 CAUSE_SW1 |

caller saved 0 to 7

Definition at line 27 of file mips.h.

caller saved 8 and 9

Definition at line 43 of file mips.h.

return value

Definition at line 21 of file mips.h.

Human readable register names wired zero

Definition at line 19 of file mips.h.

1.5.5

1.5.5